#### **MAX3956**

## 11.3Gbps Transceiver with DDM and DC-Coupled Laser Interface

#### **General Description**

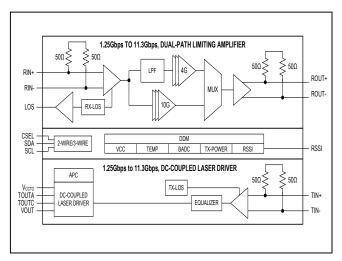

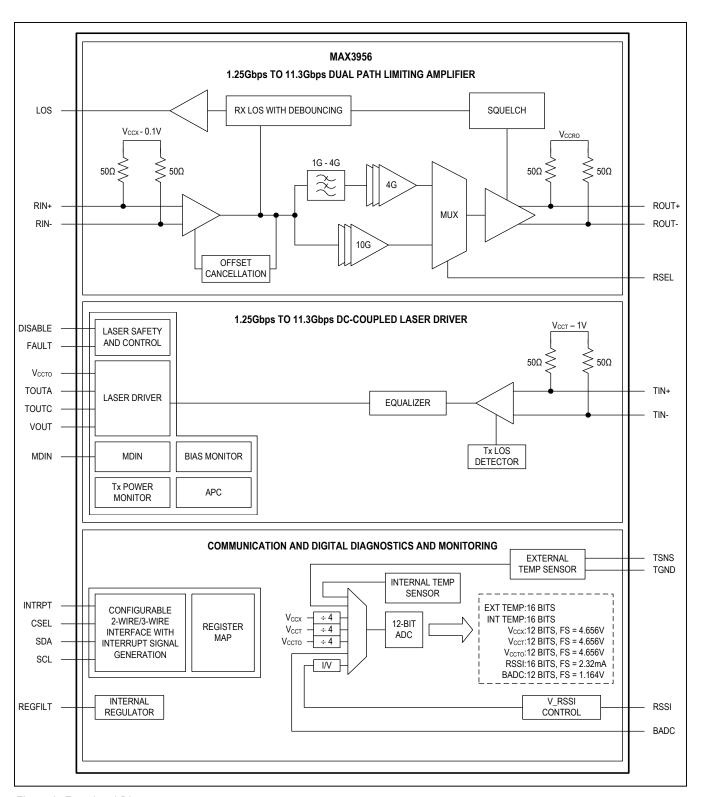

The MAX3956 is an 11.3Gbps, highly-integrated, low-power transceiver with digital diagnostics monitoring (DDM) designed for next-generation Ethernet transmission systems. The receiver incorporates a limiting amplifier and loss-of-signal (LOS) circuit. The limiting amplifier features dual-path architecture optimizing the performance for signals up to 4.25Gbps and up to 11.3Gbps, respectively. The transmitter incorporates Maxim's proprietary DC-coupled laser driver interface and closed-loop control of laser average power. This part is optimized to enable 0.8W maximum power dissipation target of SFP+ MSA based modules.

The MAX3956 supports differential AC-coupled signaling with  $50\Omega$  termination at Rx input, Rx output, and Tx input. The Tx output is a DC-coupled  $25\Omega$  laser diode interface with dedicated pins for the laser anode (TOUTA) and the laser cathode (TOUTC).

An integrated 12-bit analog-to-digital converter (ADC) is utilized to provide digital monitors of internal/external temperature,  $V_{CC}$ , and received signal strength indication (RSSI). The MAX3956's digital monitors and the use of a 2-wire or 3-wire slave interface enables configuration through a digital-only microcontroller ( $\mu$ C).

The MAX3956 operates from a single +3.3V supply and over a -40°C to +95°C temperature range and is available in a standard 5mm x 5mm, 32-pin TQFN-EP package.

### **Applications**

10GBASE-LR SFP+ Optical Transceivers

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

Low Power Consumption

- Enables < 0.8W Total SFP+ Module Power Dissipation

- 380mW Typical IC Power Dissipation at 3.3V (I<sub>LD MOD</sub> = 45mA, I<sub>BIAS</sub> = 45mA)

#### Flexibility

- Multirate up to 11.3Gbps (NRZ) Operation with Rate Select for 1.25Gbps to 4.25Gbps Operation

- Programmable Laser-Diode Modulation Current from 10mA to 85mA

- Programmable Tx Input Equalization and Rx Output Deemphasis

#### Safety and Monitoring

- Integrated Eye Safety Features with Maskable Fault and Interrupt Signal Generation

- Analog Monitors with Integrated 12-Bit ADC, Fully Supporting SFF-8472 DDM

Accurate Analog Measurements

- High-Accuracy Temperature, V<sub>CC</sub>, and RSSI Sensors

- Enables Use of Simple Digital-Only μC

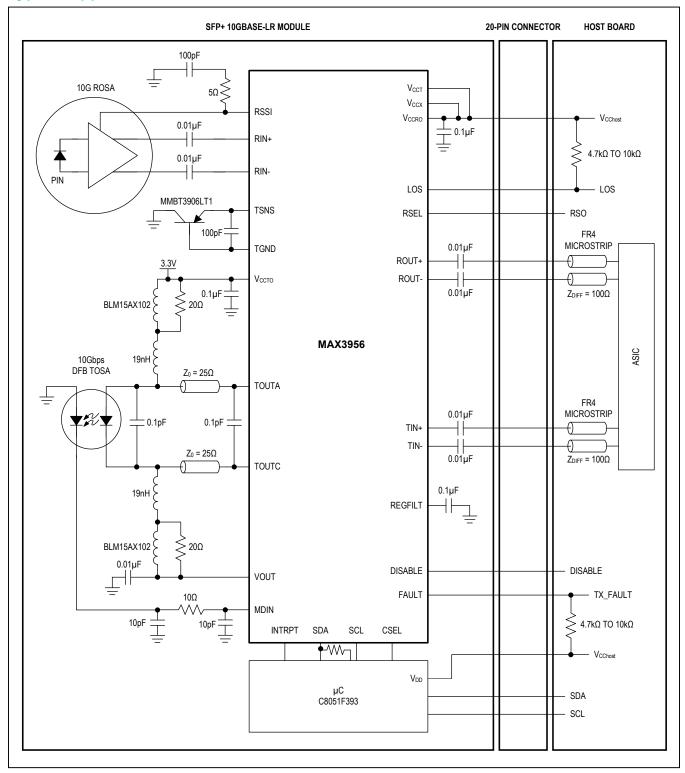

### Simplified Block Diagram

### **Absolute Maximum Ratings**

| Voltage at V <sub>CCX</sub> , V <sub>CCRO</sub> , V <sub>CCT</sub> , V <sub>CCTO</sub> | 0.3V to 4.0V              |

|----------------------------------------------------------------------------------------|---------------------------|

| Voltage at REGFILT                                                                     |                           |

| Current into V <sub>CCTO</sub>                                                         | 15mA to +180mA            |

| Current into REGFILT                                                                   | 15mA to +15mA             |

| Current into TOUTA and TOUTC                                                           | +150mA                    |

| Current into VOUT                                                                      | 2mA to +90mA              |

| Current into TIN+, TIN-, RIN+, and RIN                                                 | 15mA to +15mA             |

| Current into ROUT+ and ROUT                                                            | 30mA to +30mA             |

| Voltage at TIN+, TIN-, RIN+, RIN-, LOS,                                                |                           |

| DISABLE, FAULT, MDIN,                                                                  |                           |

| RSSI, SCL, SDA, INTRPT, and CSEL -0.                                                   | .3V to $(V_{CCX} + 0.3V)$ |

| Voltage at TSNS, TGND                                 | 0.3V to 1.2V                  |

|-------------------------------------------------------|-------------------------------|

| Voltage at BADC, I.C.                                 | 0.3V to 2V                    |

| Voltage at TOUTA(V <sub>CCTO</sub> - 1.3V) to         |                               |

| Voltage at TOUTC and VOUT0.3V to                      | to (V <sub>CCTO</sub> - 0.4V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                               |

| TQFN (derate 34.5mW/°C above +70°C)                   | 2759mW                        |

| Junction Temperature                                  | +150°C                        |

| Storage Temperature Range                             | 55°C to +150°C                |

| Lead Temperature (soldering, 10s)                     | +300°C                        |

| Soldering Temperature (reflow)                        | +260°C                        |

|                                                       |                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

#### **TQFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......29°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )........1.7°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C}$  to +95°C. Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCTO} = 3.3V$ , 14Ω single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                                                                 | MIN | TYP | MAX | UNITS             |

|--------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|

| Power-Supply Current                             | I <sub>CC</sub>      | Excludes current through TOUTC and TOUTA; $I_{LD\_MOD}$ = 60mA, $I_{LD\_DC}$ = 40mA, and SET_CML[4:0] = 3d |     | 105 | 130 | mA                |

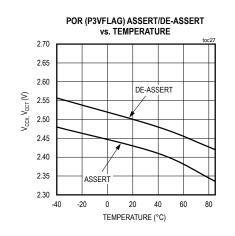

| Power-On-Reset (Enable Part)                     | V <sub>POR_DE</sub>  |                                                                                                            |     | 2.5 |     | V                 |

| Power-On-Reset (Disable Part)                    | V <sub>POR_AS</sub>  |                                                                                                            |     | 2.4 |     | V                 |

| RX INPUT SPECIFICATION                           |                      |                                                                                                            |     |     |     |                   |

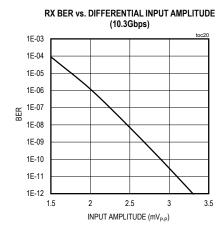

| Input Sensitivity for BER < 10 <sup>-12</sup>    | V <sub>RIN_MIN</sub> | 2 <sup>31</sup> -1 PRBS at 11.3Gbps                                                                        |     | 3   |     | $mV_{P-P}$        |

| Differential Input Resistance                    | R <sub>RIN</sub>     |                                                                                                            |     | 100 |     | Ω                 |

| RX OUTPUT SPECIFICATION (S                       | SET_RXDE[2:0] =      | 0xx)                                                                                                       |     |     |     |                   |

| Differential Output Voltage<br>Programming Range | V <sub>ROUT</sub>    | See Table 7 for more information                                                                           | 450 |     | 800 | mV <sub>P-P</sub> |

| Differential Output Voltage when Squelched       | V <sub>ROUT</sub>    | SQ_EN = 1                                                                                                  |     | 5   |     | mV <sub>P-P</sub> |

| Differential Output Resistance                   | R <sub>ROUT</sub>    |                                                                                                            |     | 100 |     | Ω                 |

### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C}$  to +95°C. Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ , 14Ω single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                                     | SYMBOL                         | CONDI                                                                            | TIONS                        | MIN | TYP  | MAX | UNITS               |  |

|-----------------------------------------------|--------------------------------|----------------------------------------------------------------------------------|------------------------------|-----|------|-----|---------------------|--|

| 5                                             |                                | 10.3Gbps (Notes 3,                                                               | 4, and 5)                    |     | 4.6  | 10  |                     |  |

| Deterministic Jitter                          | DJ                             | 11.3Gbps (Notes 3,                                                               | 11.3Gbps (Notes 3, 4, and 5) |     | 5.6  | 11  | ps <sub>P-P</sub>   |  |

| Random Jitter                                 | RJ                             | V <sub>RIN</sub> = 60mV <sub>P-P</sub> at<br>11111 00000 patterr<br>10d (Note 3) |                              |     | 0.25 | 0.4 | ps <sub>RMS</sub>   |  |

| ROUT Rise/Fall Time                           | t <sub>R</sub> /t <sub>F</sub> | 20% to 80%, RSEL<br>(Notes 3 and 5) 111                                          |                              |     | 27   | 35  | ps                  |  |

| RX OMA BASED LOSS-OF-SIG                      | NAL (LOS) SPEC                 | IFICATION (Notes 3                                                               | and 7)                       |     |      |     | •                   |  |

| Assert/Deassert Time                          |                                | (Note 6)                                                                         |                              | 2.3 |      | 80  | μs                  |  |

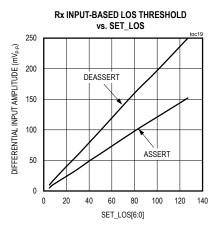

| 1001 10 10                                    |                                | SET_LOS[6:0]                                                                     | Assert level                 | 6   | 10   | 16  | .,                  |  |

| LOS Low Level Setting                         |                                | = 8d                                                                             | Deassert level               | 12  | 16.7 | 23  | mV <sub>P-P</sub>   |  |

| 1.00.11                                       |                                | SET_LOS[6:0] =                                                                   | Assert level                 |     | 48   |     | .,                  |  |

| LOS Medium Level Setting                      |                                | 38d                                                                              | Deassert level               |     | 78   |     | mV <sub>P-P</sub>   |  |

| 1001511 10 15                                 |                                | SET_LOS[6:0] = /                                                                 | Assert level                 |     | 121  |     | .,                  |  |

| LOS High Level Setting                        |                                | 101d                                                                             | Deassert level               |     | 197  |     | - mV <sub>P-P</sub> |  |

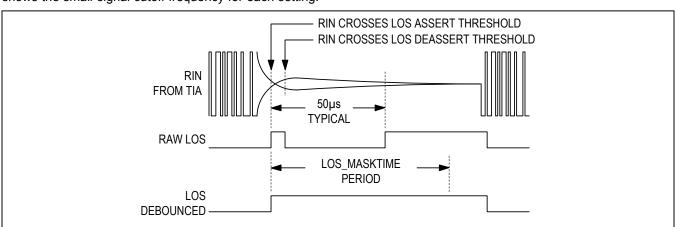

| LOS Output Masking Time                       |                                | LOS_MASKTIME = 0d                                                                |                              |     | 0    |     |                     |  |

| Range                                         |                                | LOS_MASKTIME = 127d                                                              |                              |     | 4.6  |     | ms                  |  |

| LOS Output Masking Time<br>Setting Resolution |                                | (Note 8)                                                                         |                              |     | 36   |     | μs                  |  |

| TX INPUT SPECIFICATION                        |                                |                                                                                  |                              |     |      |     | 1                   |  |

| Differential Input Resistance                 | R <sub>TIN</sub>               |                                                                                  |                              |     | 100  |     | Ω                   |  |

| LASER DC CURRENT GENERA                       | TOR (Note 9)                   |                                                                                  |                              |     |      |     |                     |  |

| Maximum DC-ON Current                         | I <sub>DC_MAX</sub>            | Current into VOUT                                                                | oin                          | 57  |      |     | mA                  |  |

| Minimum DC-ON Current                         | I <sub>DC_MIN</sub>            | Current into VOUT                                                                | oin                          |     | 0.7  | 1   | mA                  |  |

| Maximum DC-OFF Current                        | I <sub>DC_OFF</sub>            | Laser current into V Tx output disabled                                          | OUT pin when                 |     |      | 0.1 | mA                  |  |

| LASER MODULATOR OUTPUT                        | $(TX_EQ[1:0] = 00$             | 0) (Note 10)                                                                     |                              |     |      |     |                     |  |

| Maximum Modulation ON-<br>Current             | ILD_MOD_MAX                    | Current into TOUTC, external 10Ω differential load                               |                              | 85  |      |     | mA                  |  |

| Minimum Modulation ON-<br>Current             | ILD_MOD_MIN                    | Current into TOUTC, external 10Ω differential load                               |                              |     |      | 10  | mA                  |  |

| Modulation Output Termination                 | R <sub>TOUT</sub>              | Single-ended resistance                                                          |                              |     | 25   |     | Ω                   |  |

| Maximum Modulation OFF-<br>Current            | I <sub>LD_MOD_OFF</sub>        | Current into TOUTC pin when Tx output disabled                                   |                              |     |      | 0.1 | mA                  |  |

| Modulation Current DAC Stability              |                                | 10mA < I <sub>LD_MOD</sub> < and 11)                                             | 85mA (Notes 3                |     | 1.5  | 4   | %                   |  |

### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C}$  to +95°C. Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ , 14Ω single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                              | SYMBOL                         | CONDITIONS                                                                                                                                                              | MIN                                                   | TYP                          | MAX       | UNITS             |

|----------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------|-----------|-------------------|

| LASER MODULATOR OUTPUT (Notes 3 and 4) | T (TX_EQ[1:0] = 00             | 0, 10mA < I <sub>LD_MOD</sub> < 85mA, V <sub>TIN</sub> = 150 t                                                                                                          | to 1000m                                              | V <sub>P-P</sub> diffe       | ential an | nplitude)         |

| Modulation Current Rise/Fall Time      | t <sub>R</sub> /t <sub>F</sub> | 20% to 80%, 11111 00000 pattern                                                                                                                                         |                                                       | 24                           | 35        | ps                |

| Deterministic litter                   | DI                             | 10.3Gbps                                                                                                                                                                |                                                       | 5                            | 11        |                   |

| Deterministic Jitter                   | DJ                             | 11.3Gbps                                                                                                                                                                |                                                       | 5                            | 11        | ps <sub>P-P</sub> |

| Random Jitter                          | RJ                             | 11111 00000 pattern                                                                                                                                                     |                                                       | 0.23                         | 0.55      | ps <sub>RMS</sub> |

| APC LOOP OPERATION SPEC                | IFICATION                      |                                                                                                                                                                         |                                                       |                              |           |                   |

| MD Average Current Range               | IMDIN_AVG                      | Average current sunk from MDIN pin                                                                                                                                      | 50                                                    |                              | 2000      | μA                |

| Initialization Time                    | t_init                         | I <sub>DC</sub> = 40mA, I <sub>MOD</sub> = 60mA, I <sub>DC_init</sub> = 0mA, ER = 9dB, time from restart to I <sub>DC</sub> and I <sub>MOD</sub> at 90% of steady state |                                                       | 0.1                          |           | ms                |

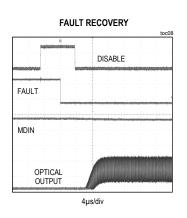

| TIMING REQUIREMENTS (Note              | e 3)                           |                                                                                                                                                                         |                                                       |                              |           |                   |

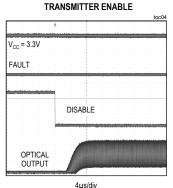

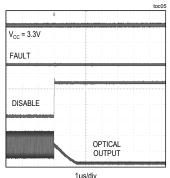

| DISABLE Assert Time                    | t_off                          | Time from rising edge of DISABLE input signal to 10% of I <sub>DC</sub> and I <sub>MOD</sub>                                                                            |                                                       | 1.5                          | 10        | μs                |

| DISABLE Negate Time                    | t_on                           | Time from falling edge of DISABLE to I <sub>DC</sub> and I <sub>LD_MOD</sub> at 90% of steady state when FAULT = low before reset                                       |                                                       | 8                            |           | μs                |

| FAULT Reset Time                       | t_recovery                     | Time from negation of latched fault using DISABLE to I <sub>LD_MOD</sub> + I <sub>DC</sub> at 90% of steady state                                                       | DISABLE to I <sub>LD MOD</sub> + I <sub>DC</sub> at 8 |                              |           | μs                |

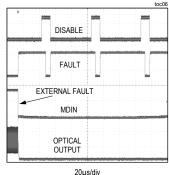

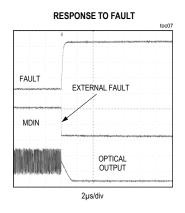

| FAULT Assert Time                      | t_fault                        | Time from fault to TX_FAULT = high,<br>$C_{FAULT} \le 20pF$ , $R_{FAULT} = 4.7k\Omega$                                                                                  |                                                       | 1                            | 3         | μs                |

| DISABLE to Reset Time                  |                                | Time DISABLE must be held high to reset fault                                                                                                                           | 4                                                     |                              |           | μs                |

| SAFETY FEATURES                        |                                |                                                                                                                                                                         |                                                       |                              |           |                   |

| Fault Assert Threshold at VOUT         |                                | FAULT always occurs for VOUT < V <sub>CCTO</sub> - 2.8V                                                                                                                 |                                                       | V <sub>CCTO</sub><br>- 2.8V  |           | V                 |

| Fault Deassert Threshold at VOUT       |                                | FAULT never occurs for VOUT ≥ V <sub>CCTO</sub> - 2.0V                                                                                                                  |                                                       | V <sub>CCTO</sub><br>- 2.0V  |           | ٧                 |

| Fault Assert Threshold at TOUTC        |                                | FAULT always occurs for V <sub>TOUTC</sub> < 0.24V                                                                                                                      |                                                       | 0.24                         |           | V                 |

| Fault Deassert Threshold at TOUTC      |                                | FAULT never occurs for V <sub>TOUTC</sub> ≥ 0.58V                                                                                                                       |                                                       | 0.58                         |           | V                 |

| Fault Threshold at TOUTA               |                                | FAULT always occurs for V <sub>TOUTA</sub> < V <sub>CCTO</sub> - 1.85V                                                                                                  |                                                       | V <sub>CCTO</sub><br>- 1.85V |           | V                 |

### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C}$  to +95°C. Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ , 14Ω single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                               | SYMBOL                                   | CONDITIONS                                                                                          | MIN  | TYP                          | MAX  | UNITS |

|-----------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------------------------------|------|-------|

| Fault Deassert Threshold at TOUTA       |                                          | FAULT never occurs for V <sub>TOUTA</sub> ≥ V <sub>CCTO</sub> - 1.34V                               |      | V <sub>CCTO</sub><br>- 1.34V |      | V     |

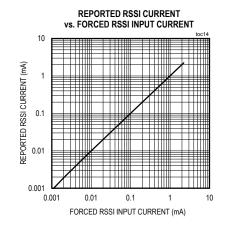

| RSSI MONITOR                            |                                          |                                                                                                     |      |                              |      |       |

| ADC Resolution                          |                                          |                                                                                                     |      | 16                           |      | bits  |

| LSb Size                                |                                          |                                                                                                     |      | 35.5                         |      | nA    |

| RSSI Input Current Range                |                                          |                                                                                                     | 1    |                              | 2000 | μA    |

| RSSI Offset Current                     |                                          |                                                                                                     |      | 50                           |      | nA    |

| RSSI Offset Current Stability           |                                          | (Notes 3 and 12)                                                                                    | -120 |                              | +150 | nA    |

| RSSI Gain Error                         |                                          | (Note 3)                                                                                            | -4   |                              | +4   | %     |

| TX POWER MONITOR                        |                                          |                                                                                                     |      |                              |      |       |

| Tx Power Monitor Accuracy               |                                          | Average current into MDIN pin 50µA < I <sub>MDIN_AVG</sub> < 2mA, excluding tracking error (Note 3) | -25  |                              | +25  | %     |

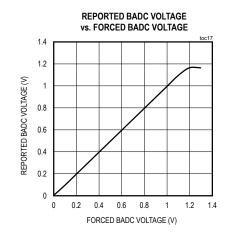

| BADC MONITOR                            |                                          |                                                                                                     |      |                              |      |       |

| Gain Error                              |                                          |                                                                                                     | -2   |                              | +2   | %     |

| ADC Full Scale                          |                                          |                                                                                                     |      | 1.164                        |      | V     |

| ADC Resolution                          |                                          |                                                                                                     |      | 12                           |      | bits  |

| ADC LSB Size                            |                                          |                                                                                                     |      | 284                          |      | μV    |

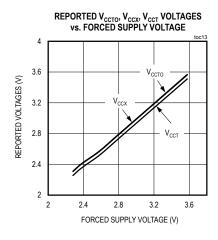

| SUPPLY VOLTAGE MONITOR (                | V <sub>CCX</sub> , V <sub>CCRO</sub> , a | nd V <sub>CCT</sub> )                                                                               |      |                              |      |       |

| Supply Voltage Monitor<br>Accuracy      |                                          | V <sub>CCX</sub> = V <sub>CCRO</sub> = V <sub>CCT</sub> > V <sub>POR_DE</sub>                       | -2   |                              | +2   | %     |

| ADC Resolution                          |                                          |                                                                                                     |      | 12                           |      | bits  |

| ADC LSb Size                            |                                          |                                                                                                     |      | 1.137                        |      | mV    |

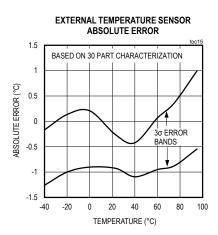

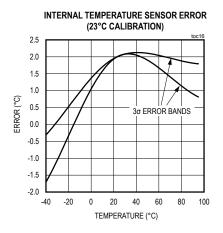

| TEMPERATURE SENSOR                      |                                          |                                                                                                     |      |                              |      |       |

| External Temperature Sensor<br>Accuracy |                                          | Measured with a single PNP device (Note 3)                                                          | -2   |                              | +2   | °C    |

| DIGITAL INPUTS (SDA, SCL, CS            | SEL, DISABLE,                            | RSEL)                                                                                               | ı    |                              |      |       |

| Minimum Input Voltage High              | V <sub>IH</sub>                          |                                                                                                     |      | 1.6                          |      | V     |

| Maximum Input Voltage High              | V <sub>IH</sub>                          |                                                                                                     |      | V <sub>CC</sub>              |      | V     |

| Minimum Input Voltage Low               | V <sub>IL</sub>                          |                                                                                                     |      | 0                            |      | V     |

### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C}$  to +95°C. Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ , 14Ω single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                                    | SYMBOL           | CONDITIONS                                                                     | MIN                     | TYP               | MAX | UNITS |

|----------------------------------------------|------------------|--------------------------------------------------------------------------------|-------------------------|-------------------|-----|-------|

| Maximum Input Voltage Low                    | V <sub>IL</sub>  |                                                                                |                         | 0.8               |     | V     |

| Input Hysteresis                             | V <sub>HYS</sub> |                                                                                |                         | 80                |     | mV    |

| Input Leakage Current High (SDA, DISABLE)    | I <sub>IH</sub>  | Input connected to V <sub>CCRO</sub>                                           | -10                     |                   | +10 | μA    |

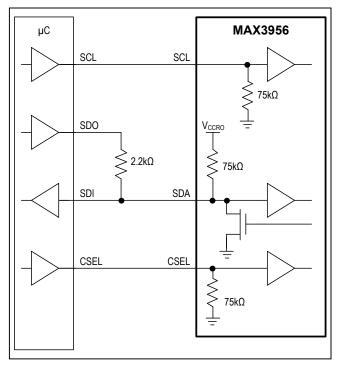

| Input Leakage Current High (SCL, CSEL, RSEL) | I <sub>IH</sub>  | Input connected to $V_{CCRO}$ , internal 75k $\Omega$ pulldown                 | 20                      | 44                | 100 | μA    |

| Input Leakage Current Low (SCL, CSEL, RSEL)  | I <sub>IL</sub>  | Input connected to GND                                                         | -10                     |                   | +10 | μA    |

| Input Leakage Current Low (SDA)              | I <sub>IL</sub>  | Input connected to GND, internal 75kΩ pullup                                   | 20                      | 44                | 100 | μA    |

| Input Leakage Current Low (DISABLE)          | I <sub>IL</sub>  | Input connected to GND, internal 7.5kΩ pullup                                  | 200                     | 450               | 800 | μA    |

| DIGITAL OPEN-DRAIN OUTPUT                    | (SDA, LOS, and   | FAULT) (Note 14)                                                               |                         |                   |     |       |

| Output Low Voltage                           | V <sub>OL</sub>  | External pullup is between 4.7k $\Omega$ and 10k $\Omega$ to V <sub>CCRO</sub> |                         |                   | 0.4 | V     |

| Output High Voltage                          | V <sub>OH</sub>  | External pullup is between 4.7k $\Omega$ and 10k $\Omega$ to V <sub>CCRO</sub> | V <sub>CCRO</sub>       | V <sub>CCRO</sub> |     | V     |

| DIGITAL CMOS OUTPUT (INTRI                   | PT, LOS, and FA  | ULT) (Note 14)                                                                 | •                       |                   |     |       |

| Output Low Voltage                           | V <sub>OL</sub>  | I <sub>OL</sub> = 1mA                                                          |                         |                   | 0.4 | V     |

| Output High Voltage                          | $V_{OH}$         | I <sub>OH</sub> = 1mA                                                          | V <sub>CCRO</sub> - 0.4 |                   |     | V     |

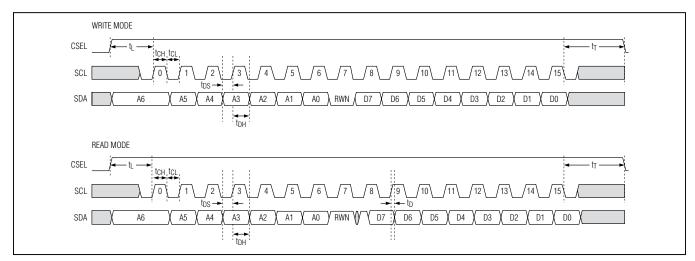

| 3-WIRE TIMING SPECIFICATION                  | NS (Figure 3)    |                                                                                |                         |                   |     |       |

| Maximum SCL Clock<br>Frequency               | fscl             |                                                                                |                         | 1000              |     | kHz   |

| Minimum SCL Pulse Width High                 | t <sub>CH</sub>  |                                                                                |                         | 500               |     | ns    |

| Minimum SCL Pulse Width Low                  | t <sub>CL</sub>  |                                                                                |                         | 500               |     | ns    |

| SDA Setup Time                               | t <sub>DS</sub>  |                                                                                |                         | 100               |     | ns    |

| SDA Hold Time                                | t <sub>DH</sub>  |                                                                                |                         | 100               |     | ns    |

| SCL Rise to SDA Propagation Time             | t <sub>D</sub>   |                                                                                |                         | 12                |     | ns    |

| Minimum CSEL Pulse Width Low                 | t <sub>CSW</sub> |                                                                                |                         | 500               |     | ns    |

| CSEL Leading Time Before the First SCL Edge  | tL               |                                                                                |                         | 500               |     | ns    |

| CSEL Trailing Time After the Last SCL Edge   | t <sub>T</sub>   |                                                                                |                         | 500               |     | ns    |

#### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}$ . Typical values are at  $V_{CCX} = V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ ,  $14\Omega$  single-ended load for TOUTC/TOUTA, and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

| PARAMETER                                               | SYMBOL                          | CONDITIONS                                                                       | MIN | TYP                       | MAX | UNITS |

|---------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|-----|---------------------------|-----|-------|

| Maximum Capacitive Load SDA, SCL                        | C <sub>b</sub>                  | Total bus capacitance on one line with $4.7 k\Omega$ pullup from SDA to $V_{CC}$ |     | 20                        |     | pF    |

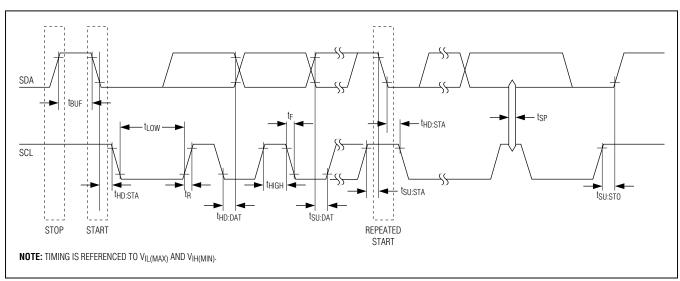

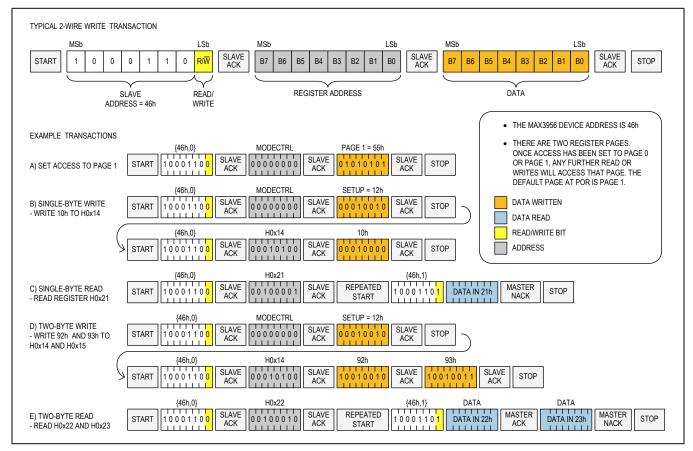

| 2-WIRE TIMING SPECIFICATION                             | NS (Figure 5)                   |                                                                                  |     |                           |     |       |

| Maximum SCL Clock<br>Frequency                          | fSCL                            |                                                                                  |     | 400                       |     | kHz   |

| Minimum SCL Pulse Width High                            | t <sub>CH</sub>                 |                                                                                  |     | 1.3                       |     | μs    |

| Minimum SCL Pulse Width Low                             | t <sub>CL</sub>                 |                                                                                  |     | 0.6                       |     | μs    |

| Minimum Bus Free Time Between STOP and START Condition  | t <sub>BUF</sub>                |                                                                                  |     | 1.3                       |     | μs    |

| Minimum STOP Setup Time                                 | tsu_sto                         |                                                                                  |     | 600                       |     | ns    |

| Minimum START Setup Time                                | tsu_sta                         |                                                                                  |     | 600                       |     | ns    |

| Minimum START Hold Time                                 | t <sub>HD_STA</sub>             |                                                                                  |     | 600                       |     | ns    |

| Minimum SDA Setup Time                                  | t <sub>HD_DAT</sub>             |                                                                                  |     | 100                       |     | ns    |

| Minimum SDA Hold Time                                   |                                 | Receive                                                                          |     | 0                         |     |       |

| Minimum SDA Hold Time                                   | thd_dat                         | Transmit                                                                         | 300 |                           |     | ns    |

| Minimum SCL and SDA Rise and Fall Time                  | t <sub>R</sub> , t <sub>F</sub> | (Note 15)                                                                        |     | 20 +<br>0.1C <sub>b</sub> |     | ns    |

| Maximum Spike Pulse Width<br>Suppressed by Input Filter | t <sub>SP</sub>                 |                                                                                  |     | 50                        |     | ns    |

| Maximum Capacitive Load SDA, SCL                        | C <sub>b</sub>                  | Total bus capacitance on one line                                                |     | 20                        |     | pF    |

- **Note 2:** Limits are 100% tested at  $T_A = +25^{\circ}C$  (and/or  $T_A = +95^{\circ}C$ ). Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

- Note 3: Guaranteed by design and characterization.

- **Note 4:** A repeating 2<sup>7</sup> PRBS + 72 zeros and 2<sup>7</sup> PRBS (inverted) + 72 ones pattern is used. Deterministic jitter is defined as the arithmetic sum of pulse-width distortion (PWD) and pattern-dependent jitter (PDJ). Source DJ is removed from the measurement.

- Note 5:  $V_{RIN}$  is  $30mV_{P-P}$  to  $1.2V_{P-P}$  differential amplitude, SET\_CML = 10d. Input data transition time 21ps (20% to 80%).

- Note 6: LOS must not assert if the input data is invalid for less than 2.3µs. The LOS must assert, if the data is invalid for more than 80µs. The signal at the input will be switched between two amplitudes Signal ON, and Signal OFF.

- 1) Receiver operates at sensitivity level plus 1dB power penalty

- A) Signal\_OFF = 0; Signal\_ON = (+8dB) + 10log(min\_assert\_level)

- B) Signal\_ON = (+1dB) + 10log(max\_deassert\_level); Signal\_OFF = 0

- 2) Receiver operates at overload

- Signal\_OFF = 0; Signal\_ON =  $1.2V_{P-P}$

- Note 7: LOS hysteresis (10 × Log(V<sub>LOS-DEASSERT</sub>/V<sub>LOS-ASSERT</sub>)dB) is designed to be > 1.25dB for SET\_LOS[6:0] DAC code from 8d to 101d. LOS is characterized with a 2<sup>23</sup>-1 PRBS pattern for 11.3Gbps and a K28.5 pattern for 1.25Gbps operation

- Note 8: Output of a TIA in case of loss of light, see Figure 7.

- Note 9:  $I_{LD\_DC} = I_{DC} + 0.5 \times I_{MOD} \times R/(50 + R)$ , where  $I_{LD\_DC}$  is the effective laser DC current,  $I_{DC}$  is the DC DAC current,  $I_{MOD}$  is the modulation DAC current, and R is the differential laser load resistance. Example: For R =  $5\Omega$ ,  $I_{LD\_DC} = I_{DC} + 0.045 \times I_{MOD}$ . The required compliance range for VOUT, while Tx output is enabled, is  $V_{CCTO} 1V$  to  $V_{CCTO} 2V$ .

#### **Electrical Characteristics (continued)**

$(V_{CCX} = V_{CCRO} = V_{CCT} = 2.85V \text{ to } 3.47V, V_{CCTO} = 2.97V \text{ to } 3.47V, V_{GND} = 0V, T_A = -40^{\circ}\text{C} \text{ to } +95^{\circ}\text{C}$ . Typical values are at  $V_{CCX} = V_{CCX} = V_$  $V_{CCRO} = V_{CCT} = V_{CCTO} = 3.3V$ ,  $14\Omega$  single-ended load for TOUTC/TOUTA, and  $T_A = +25$ °C, unless otherwise noted. See Figure 1 for electrical setup.) (Note 2)

- Note 10: $I_{LD\ MOD} = I_{MOD} \times 50/(50 + R)$ , where  $I_{LD\ MOD}$  is the effective laser modulation current,  $I_{MOD}$  is the modulation DAC current, and R is the differential laser load resistance. Example: For R =  $5\Omega$ ,  $I_{LD\ MOD}$  =  $0.91 \times I_{MOD}$ .

- Note 11: Stability is defined as [(I<sub>MEASURED</sub>) (I<sub>REFERENCE</sub>)]/(I<sub>REFERENCE</sub>) over the listed current/temperature range and V<sub>CCT</sub> = V<sub>CCX</sub> = V<sub>CCRO</sub> = V<sub>CCREF</sub> ±5%, V<sub>CCREF</sub> = 3.3V. Reference current measured at V<sub>CCREF</sub> and T<sub>REF</sub> = +25°C.

- Note 12: Stability is defined as [(I<sub>MEASURED</sub>) (I<sub>REFERENCE</sub>) over the listed temperature range and supply range. Reference current measured at  $V_{CC}$  = 3.3V and  $T_{REF}$  = +25°C.

- Note 13:Calibrated at room temperature by adjusting TSNS\_INT\_OFS[15:0] (TSNS\_INT\_SCL[15:0] unchanged from default value). In order to reduce the effect of self-heating the Rx and Tx circuitry are disabled. To minimize the reported error over the full temperature range, calibration is set such that the reported result is 2°C above ambient at room temperature. In the application, self-heating may introduce additional variation.

- Note 14: For open-drain configuration FAULT\_PU\_EN = 0 and LOS\_PU\_EN = 0. For CMOS output configuration FAULT\_PU\_EN = 0 1 and LOS\_PU\_EN = 1.

- **Note 15:** $C_b$  = total capacitance of one bus line in pF.

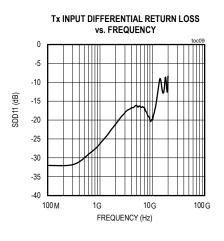

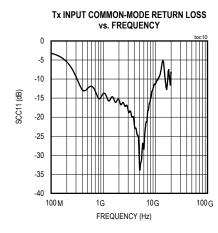

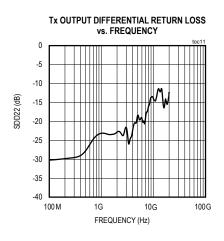

#### **Typical Operating Characteristics**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, data pattern 2^{31}-1 PRBS, unless otherwise noted.)$

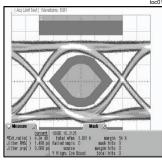

#### 10Gbps OPTICAL EYE DIAGRAM

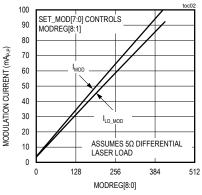

**MODULATION CURRENT vs. MODREG**

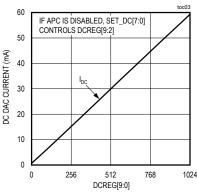

DC DAC CURRENT vs. DCREG

TRANSMITTER DISABLE

FREQUENT ASSERTION OF DISABLE

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, data pattern 2^{31}-1 PRBS, unless otherwise noted.)$

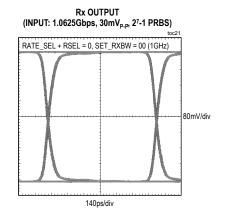

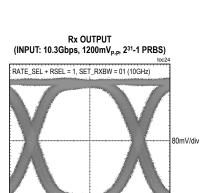

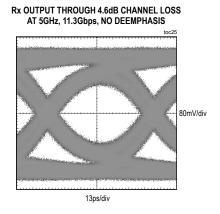

### **Typical Operating Characteristics (continued)**

( $V_{CC}$  = 3.3V,  $T_A$  = +25°C, data pattern 2<sup>31</sup>-1 PRBS, unless otherwise noted.)

12 16 20 SET\_CML[4:0]

0

DIFFERENTIAL Rx OUTPUT AMPLITUDE vs.

### **Typical Operating Characteristics (continued)**

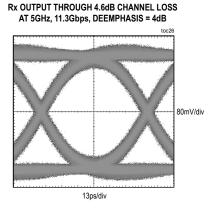

**Rx OUTPUT**

( $V_{CC}$  = 3.3V,  $T_A$  = +25°C, data pattern 2<sup>31</sup>-1 PRBS, unless otherwise noted.)

(INPUT: 4.25Gbps, 30mV<sub>P-P</sub>, 2<sup>7</sup>-1 PRBS)

toc22

RATE\_SET + RSEL = 0, SET\_RXBW = 11 (3GHz)

80mV/div

Rx OUTPUT

(INPUT: 10.3Gbps, 30mV<sub>P.P</sub>, 2<sup>31</sup>-1 PRBS)

toc23

RATE\_SET + RSEL = 1, SET\_RXBW = 01 (10GHz)

80mV/div

15ps/div

15ps/div

35ps/div

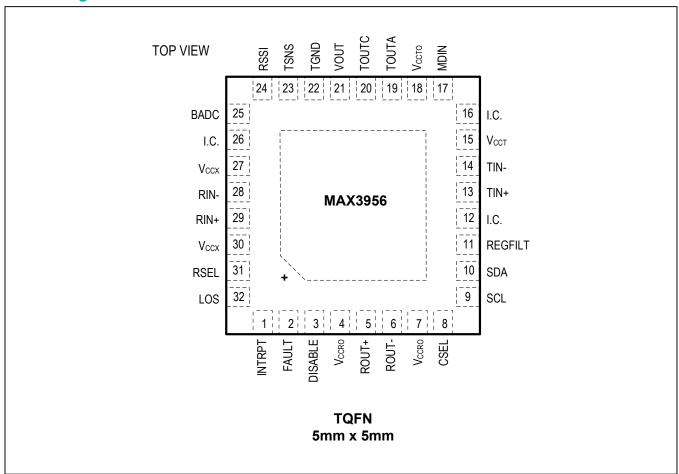

## **Pin Configuration**

### **Pin Description**

| PIN | NAME   | FUNCTION                                               | EQUIVALENT CIRCUIT                  |

|-----|--------|--------------------------------------------------------|-------------------------------------|

| 1   | INTRPT | Interrupt Output, CMOS. Programmable interrupt signal. | MAX3956 VCCRO INTRPT ESD PROTECTION |

| PIN  | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | FAULT             | Transmitter Fault, Open-Drain Output. A logic-high indicates a fault condition has been detected. It remains high even after the fault condition has been removed. A logic-low occurs when the fault condition has been removed and the fault latch has been cleared by the DISABLE signal. Connect FAULT to host $V_{CC}$ via a 4.7k $\Omega$ to $10k\Omega$ resistor. FAULT can also be configured as a CMOS output requiring no external resistor by setting the FAULT_PU_EN bit high. | MAX3956  Vccro  PROTECTION  FAULT_PU_EN  FAULT  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3    | DISABLE           | Transmitter Disable, LVTTL/CMOS input. Set to logic-low for normal operation. Logic-high or open disables both the modulation and DC current. Internally pulled up by a $7.5 \mathrm{k}\Omega$ resistor to $V_{CCRO}$ .                                                                                                                                                                                                                                                                   | MAX3956  VCCRO  VCCRO |

| 4, 7 | V <sub>CCRO</sub> | Power Supply. Provides supply voltage to the transceiver digital core and the Rx output circuitry.                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5    | ROUT+             | Differential Receiver Data Output, CML.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSD PROTECTION  50Ω SOΩ  FOUT+  ROUT+  ROUT-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6    | ROUT-             | This output has $50\Omega$ terminations to $V_{CCRO}$ . Polarity is set by the RX_POL bit.                                                                                                                                                                                                                                                                                                                                                                                                | SET_CML MAX3956                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                  | EQUIVALENT CIRCUIT                                                     |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 8   | CSEL | Chip-Select Input, CMOS. Used for 3-Wire communication. Setting CSEL to logic-high starts a cycle. Setting CSEL to logic-low ends the cycle and resets the control state machine. Internally pulled to ground by a $75 \mathrm{k}\Omega$ resistor. Set low if using 2-wire communication. | MAX3956  V <sub>CCRO</sub> V <sub>CCRO</sub> 75kΩ  ESD PROTECTION  (S) |

| 9   | SCL  | Serial-Clock Input, CMOS. Internally pulled to ground by a 75k $\Omega$ resistor.                                                                                                                                                                                                         | MAX3956  V <sub>CCRO</sub> 75kΩ  ESD PROTECTION  SCL                   |

| 10  | SDA  | Serial-Data Bidirectional I/O, CMOS. Open-drain output. This pin has a $75k\Omega$ internal pullup, but it requires an external $4.7k\Omega$ to $10k\Omega$ pullup to meet 3-wire timing specifications.                                                                                  | MAX3956  Vocro  75kΩ  Vocro  PROTECTION  SDA                           |

| PIN        | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                           | EQUIVALENT CIRCUIT                           |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 11         | REGFILT          | Internal Filter Node. Requires 0.1µF decoupling capacitor to ground.                                                                                                                                                                                                                                                               | _                                            |

| 12, 16, 26 | I.C.             | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                            | _                                            |

| 13         | TIN+             | Differential Transmitter Data Input. The                                                                                                                                                                                                                                                                                           | V <sub>CCT</sub> - 1V MAX3956  50Ω 50Ω  TIN+ |

| 14         | TIN-             | polarity is set by the TX_POL bit.                                                                                                                                                                                                                                                                                                 | TIN- ESD PROTECTION — S                      |

| 15         | V <sub>CCT</sub> | Power Supply. Provides supply voltage to the transmitter core.                                                                                                                                                                                                                                                                     | _                                            |

| 17         | MDIN             | Monitor Diode Input. Connect this pin to the cathode of the monitor diode. For transmitter power monitoring MDIN needs to be connected even for open-loop operation. External filtering on this pin should be optimized for each TOSA configuration. The Thevenin equivalent input of this pin is $40\Omega$ to $V_{CCT}$ - 1.25V. |                                              |

| PIN | NAME              | FUNCTION                                                                                                                                 | EQUIVALENT CIRCUIT            |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 18  | V <sub>ССТО</sub> | Power Supply. Provides power to the transmitter output and laser TOSA.                                                                   | MAX3956  250                  |

| 19  | TOUTA             | Inverting Modulator Current Output with $25\Omega$ back-termination. Connect to laser anode through $25\Omega$ transmission line.        | CASCODE TOUTA TOUTC  VOUT ESD |

| 20  | TOUTC             | Noninverting Modulator Current Output with 25 $\Omega$ back-termination. Connect to laser cathode through 25 $\Omega$ transmission line. | PROTECTION                    |

| 21  | V <sub>ОИТ</sub>  | Combined laser cathode current return path and sinking laser DC current output.                                                          | MAX3956 Vocto Vout            |

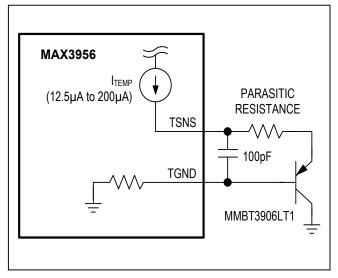

| 22  | TGND              | Connect to an external temperature sensor (cathode).                                                                                     | MAX3956 Vccx  S TOUG          |

| 23  | TSNS              | Connect to an external temperature sensor (anode).                                                                                       | TSNS TGND  ESD PROTECTION = = |

| PIN    | NAME             | FUNCTION                                                                                                                          | EQUIVALENT CIRCUIT                                              |  |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|

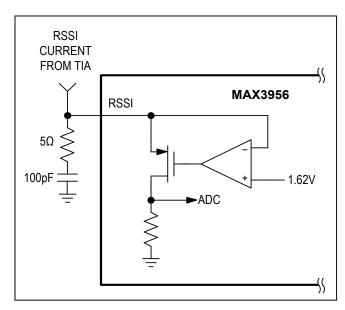

| 24     | RSSI             | Current input to main ADC for receivesignal-strength-indication (RSSI). The voltage at this pin is regulated internally to 1.62V. | RSSI MAX3956 ESD PROTECTION  1.62V                              |  |

| 25     | BADC             | Auxiliary ADC Input (≈ 1.16V full scale)                                                                                          | _                                                               |  |

| 27, 30 | V <sub>CCX</sub> | Power Supply. Provides supply voltage to the receiver core.                                                                       | _                                                               |  |

| 28     | RIN-             | Differential Receiver Data Input. Contains $50\Omega$ terminations on-chip. Connect these                                         | V <sub>CCX</sub> V <sub>CCX</sub> - 0.1V MAX3956  S0Ω 50Ω 50Ω 7 |  |

| 29     | RIN+             | inputs to the TIA outputs using coupling capacitors.                                                                              | RIN-<br>ESD PROTECTION = = = -                                  |  |

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EQUIVALENT CIRCUIT                                   |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 31  | RSEL | Rate Select, CMOS Input. Internally pulled to ground by a 75kΩ resistor. Pin is internally OR'ed with RATE_SEL bit. The output of the OR sets the Rx circuitry path to 10G for logic 1, 4G for logic 0.                                                                                                                                                                                                                                                   | RSEL VCCRO MAX3956  75kΩ  ESD PROTECTION  S          |

| 32  | LOS  | Receiver Loss-of-Signal (LOS) Output, Open Drain. This output goes to a logichigh when the level of the input signal drops below the SET_LOS register threshold. Polarity is set by LOS_POL register. The LOS circuitry can be disabled by setting LOS_EN = 0. Pull this pin to Host $V_{CC}$ via a 4.7k $\Omega$ to 10k $\Omega$ resistor. LOS can also be configured as a CMOS output requiring no external resistor by setting the LOS_PU_EN bit high. | MAX3956  VCCRO PROTECTION  LOS_PU_EN  LOS_PU_EN  LOS |

| _   | EP   | Exposed Pad. Ground. This is the only electrical connection to ground and must be soldered to circuit board ground for proper thermal and electrical performance (see the Exposed-Pad Package and Thermal Considerations section).                                                                                                                                                                                                                        | _                                                    |

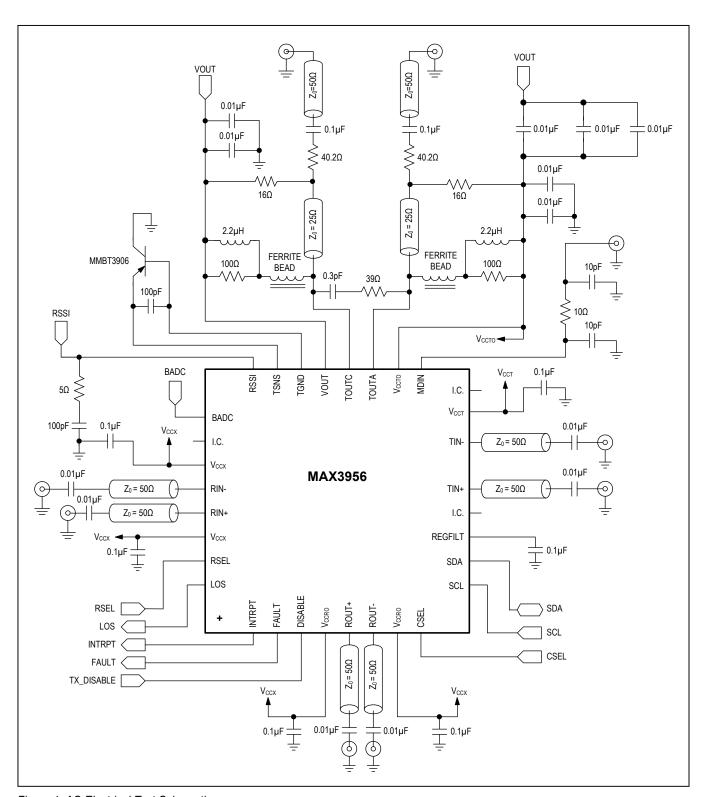

Figure 1. AC Electrical Test Schematic

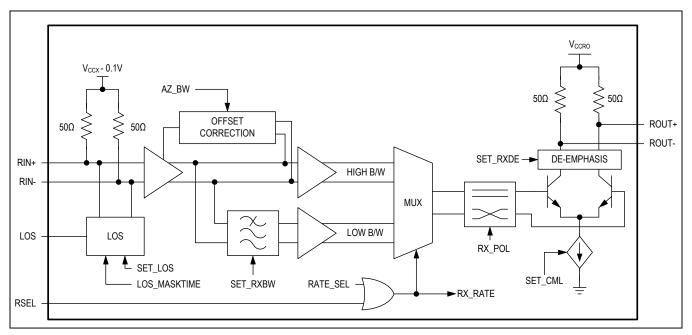

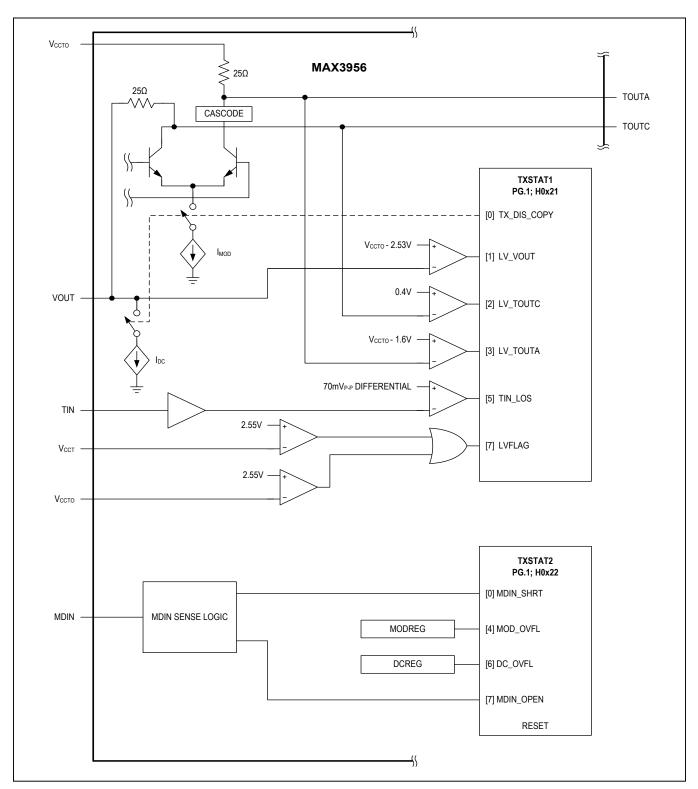

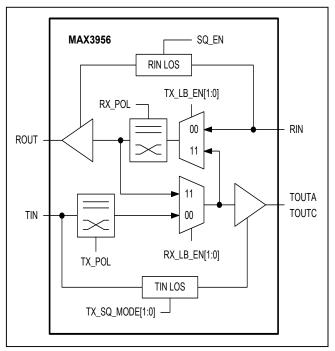

Figure 2. Functional Diagram

#### **Detailed Description**

The MAX3956 combines a high-gain limiting amplifier, laser driver, and digital diagnostics monitoring (DDM). The limiting amplifier includes offset cancellation, programmable signal detect threshold, selectable bandwidth, and deemphasis. The laser driver includes automatic power-control (APC), laser current and power measurement capability, overcurrent limiting, and fault detection. A serial control interface enables an external controller to set all parameters necessary for operation and read all monitors and status indicators. The interface accepts either 2-wire or 3-wire protocol.

The features and performance are specifically designed to be compatible with low-cost microcontrollers to provide complete SFF-8472 functionality, including laser fault detection, diagnostics, and automatic power control. The MAX3956 includes all the logic required for laser protection, control loop operation, and monitor diode (MD) current measurement.

## 1.25Gbps to 11.3Gbps Limiting Amplifier Block Description

#### **Limiting Amplifier**

The limiting amplifier consists of a multistage-multipath amplifier, offset-correction circuit, loss-of-signal circuit, and output buffer. Its low noise and high gain optimize optical performance. Configuration options (LOS threshold, LOS polarity, output amplitude, output deemphasis, and data polarity) enhance layout flexibility and ROSA compatibility.

#### **High-Speed Input Signal Path**

The inputs, RIN±, have an internal  $100\Omega$  differential termination and should be AC-coupled to the transimpedance amplifier.

#### **Offset Cancellation**

The offset cancellation loop compensates for pulse-width distortion at RIN± and internal offsets. The default small-signal low-frequency cutoff of the offset cancellation loop is 10kHz when AZ BW[1:0] is set to 01.

#### Loss-of-Signal Circuitry (LOS)

The loss-of-signal circuitry detects the amplitude of the incoming signal and compares it against a programmable threshold, which is controlled by SET\_LOS[6:0]. The range of LOS assert is  $10mV_{P-P}$  to  $121mV_{P-P}$ . Changing the LOS threshold during operation (i.e., without executing a reset) does not cause a glitch or incorrect LOS output. The detector has 2dB of hysteresis to control chatter

at the LOS output. The LOS output polarity is controlled by the LOS\_POL bit. The entire LOS circuit block can be disabled by setting LOS EN = 0.

#### **Output Drivers**

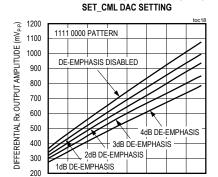

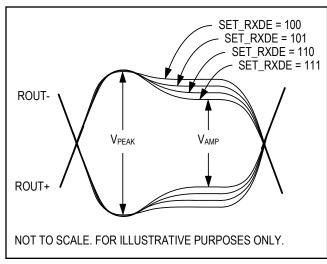

The ROUT± outputs are terminated with  $50\Omega$  to  $V_{CCRO}$ . The differential output level can be programmed between  $400\text{mV}_{P\text{-}P}$  and  $1000\text{mV}_{P\text{-}P}$  by the SET\_CML[4:0], and the output polarity can be inverted. The output can be disabled to its common-mode voltage either manually or automatically by an LOS condition (squelch through the SQ EN bit).

Deemphasis may be enabled to compensate for FR4 losses with a 10Gbps signal. If enabled, settings of 1dB, 2dB, 3dB, and 4dB deemphasis are available.

## 1.25Gbps to 11.3Gbps Laser Driver Block Description

The laser driver consists of a high-speed differential input buffer, selectable input equalizer, polarity switch buffer, laser modulator and DC current generator, monitor diode input buffer with adjustable gain, APC loop circuitry, eyesafety monitors, and DISABLE pin.

## Differential High-Speed Input Buffer with Programmable Equalization

The TIN $\pm$  inputs are internally biased and have a 100 $\Omega$  differential termination. The first amplifier stage features a programmable equalizer, controlled by TX\_EQ, to compensate for high-frequency losses including the SFP connector. The TX\_POL bit controls the signal path polarity. An active AC input signal is indicated by TIN\_LOS.

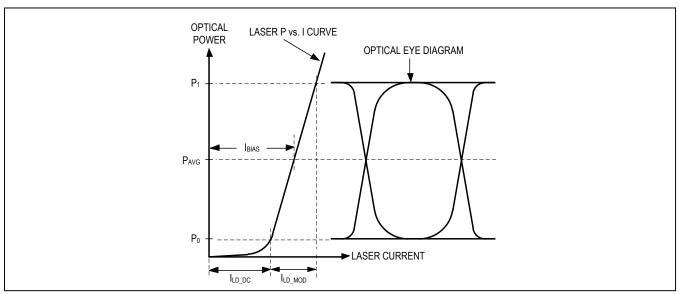

#### **Laser Modulator and DC Generator**

The laser modulator provides DC-coupled current into the cathode of the laser diode at the TOUTC pin. The modulation current amplitude is set by MODREG[8:0]. The modulation current DAC guarantees modulation amplitudes up to 85mA. The instantaneous compliance voltage for TOUTC is 0.6V to  $V_{CCTO}$  - 1V and for TOUTA is  $V_{CCTO}$  ±1V.

The VOUT pin sinks DC current from the laser's cathode. The amplitude of the laser DC current is controlled by DCREG[9:0]. The laser DC current DAC guarantees values up to 57mA.

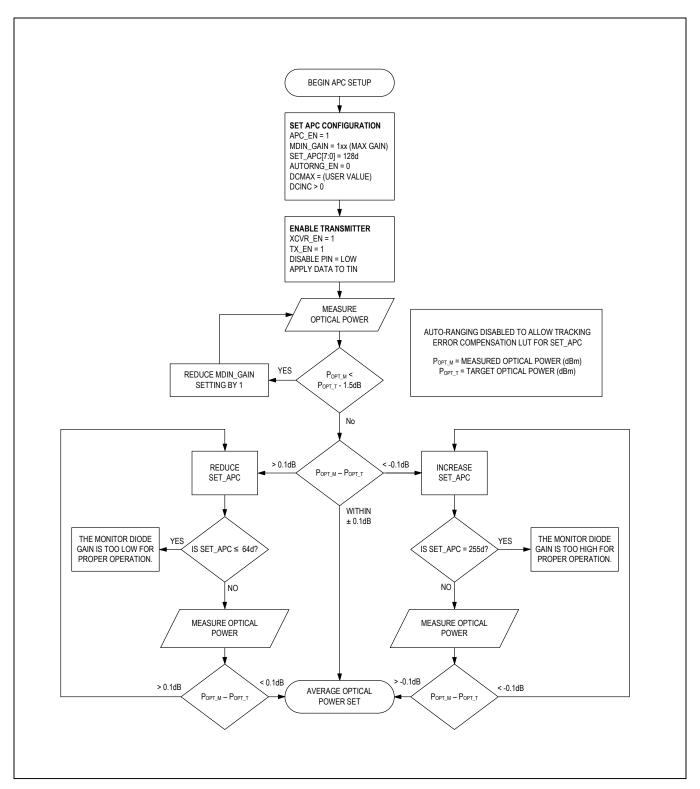

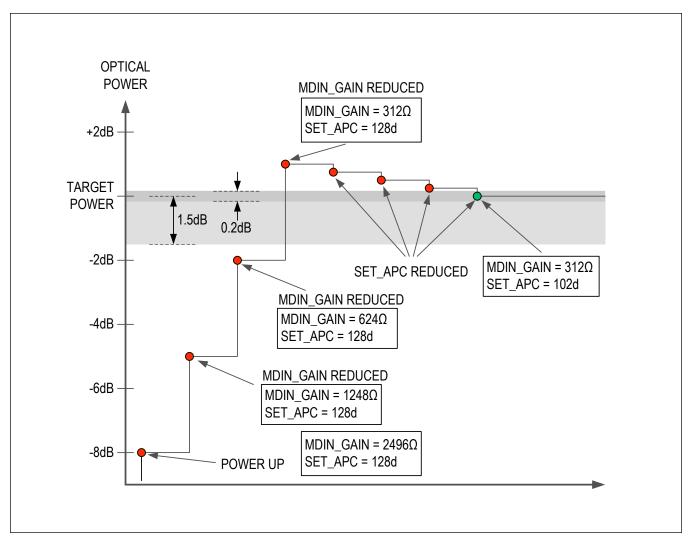

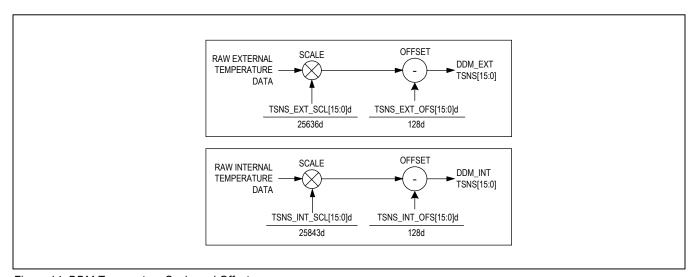

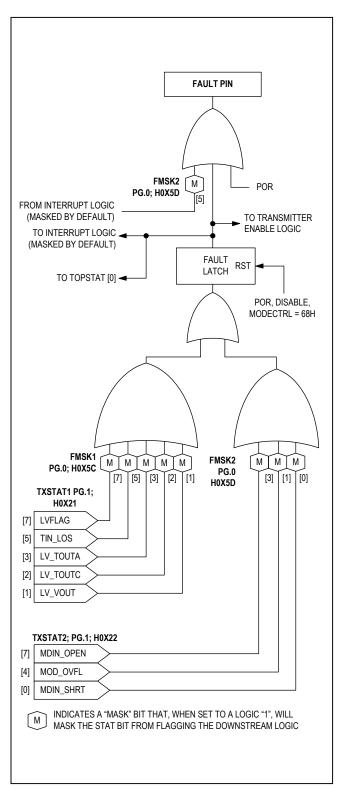

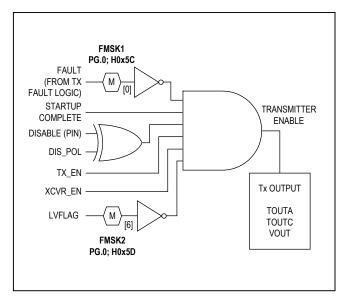

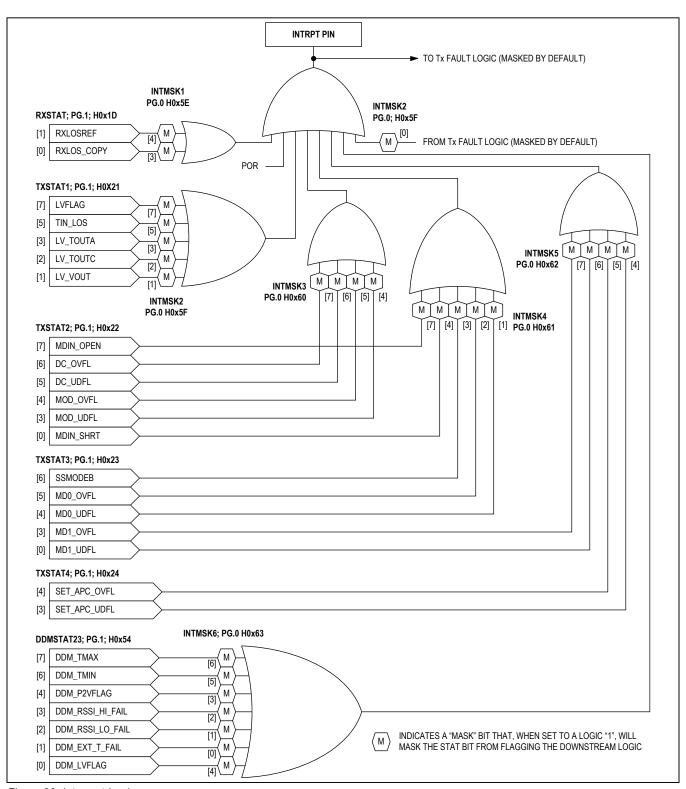

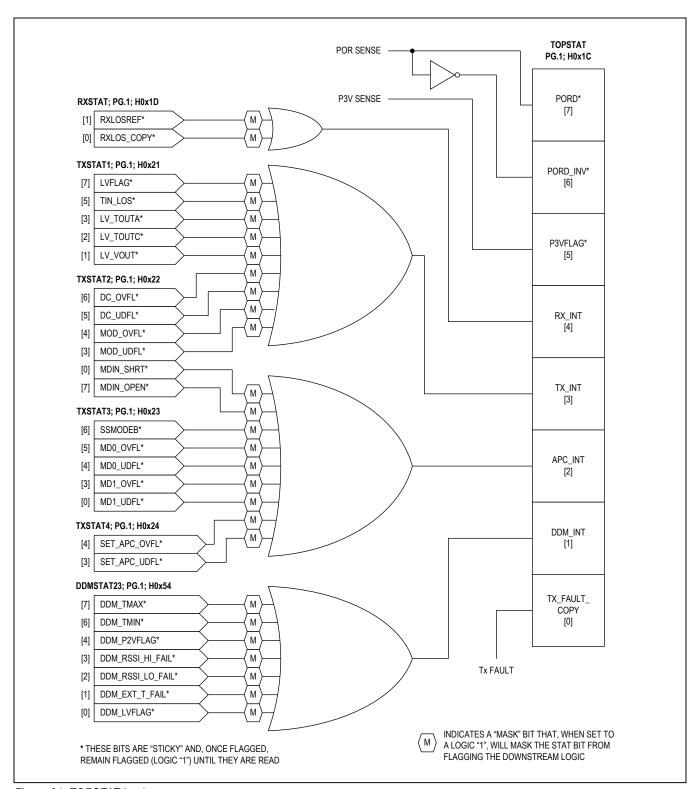

#### **Monitor Diode Current Input Buffer**